EBTKS I/O Map¶

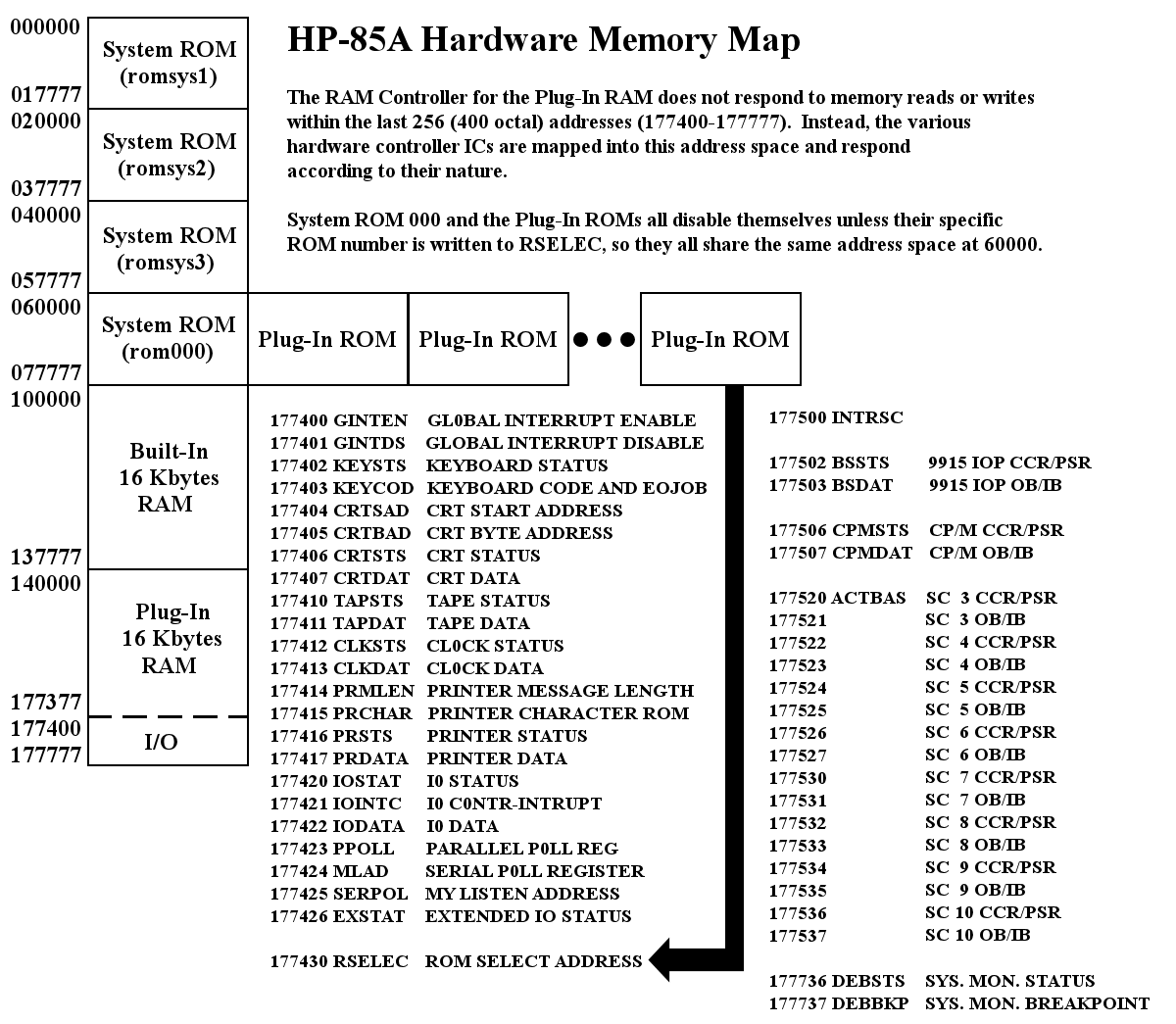

Here is another diagram taken from the HP-85 wiki authored by Everett Kaser

that is on the Groups.io web site HP 85 System ROMs: Memory Layout (and Tokens and Allocation and...)

HP86 and HP87 CRT Controller

I/O locations listed above from 177404 to 177407 are for the CRT controller used in the HP85A, HP85B and HP9915. This CRT controller is not used in the HP86 and HP87 computers, so these locations are unused. Instead, the HP 86 and HP87 have an alternative CRT controller (because the screen is 80x25 instead of 32x16) and the similar I/O registers are shown below.

Full |

I/O Offset |

||

Address |

Octal |

Hex |

|

HP86_87_CRTSAD |

177700 |

300 |

0xC0 |

HP86_87_CRTBAD |

177701 |

301 |

0xC1 |

HP86_87_CRTSTS |

177702 |

302 |

0xC2 |

HP86_87_CRTDAT |

177703 |

303 |

0xC3 |

HEYEBTKS

EBTKS reserves the following I/O addresses for communication between the AUXROMs and EBTKS. Writing a value to this mailbox I/O location tells EBTKS the function to be performed, and further information will be found in the shared memory .

Full |

I/O Offset |

||

Address |

Octal |

Hex |

|

HEYEBTKS |

177740 |

340 |

0xE0 |

Extended Memory Registers

EBTKS can provide Extended memory through the implementation of an EMC (Extended Memory Controller) and up to 256 kB of Extended memory (at the time of writing this documentation. The 256 kB may change in the future). There are two types of EMC: Master and non-Master. There can only be one Master EMC in a system. The HP85B, and all versions of HP86 and HP87 have a built in EMC Master. The HP85A does not have the capability of supporting Extended memory, and does not have an EMC Master. The EMC implements 2 pointers which can be directly read and written on the EMC Master and are write only (for direct access) on non-Master EMCs, such as EBTKS. This means that the standard implementation of an EMC non-Master does not provide diagnostic access that EBTKS required during its design phase. To remedy this EBTKS includes an additional read-only register that allows accessing the direct content of PTR2 on EBTKS. See below for details.

For indirect access through PTR1 and PTR2, EBTKS responds to reads and writes as appropriate, if the value of the selected pointer is in the address range that EBTKS is configured to respond to. Configuration comes from the CONFIG.TXT file.

If enabled, the EMC emulation has 2 pointer registers accessed as follows

Full |

I/O Offset |

||

Address |

Octal |

Hex |

|

PTR1 |

177710 |

310 |

0xC8 |

PTR1- |

177711 |

311 |

0xC9 |

PTR1+ |

177712 |

312 |

0xCA |

PTR1-+ |

177713 |

313 |

0xCB |

PTR2 |

177714 |

314 |

0xCC |

PTR2- |

177715 |

315 |

0xCD |

PTR2+ |

177716 |

316 |

0xCE |

PTR2-+ |

177717 |

317 |

0xCF |

EMC Diagnostic PTR2

In HP85B, HP86 A or B, and HP87 A or XM, the Extended Memory Controller (EMC) master is on the main board and all other EMCs are in non-master mode, including EBTKS when it is implementing Extended Memory. When an EMC is in non-master mode, the 8 I/O locations are write only, and all EMCs are written to concurrently, and update their copies of the these two underlying Pointer Registers (PTR1 and PTR2) regardless of whether the pointer values indicate memory addresses within the range that the EMC is managing. When direct addressing mode read operations are performed on these locations, only the master responds with its copy. This created a problem for the design of EBTKS, when trying to debug its operation, as the above description shows there is no way to read back PTR1 and PTR2 to check that they are being updated and modified in synchronization with the other EMCs in the system. To solve this problem (and track down a very tricky bug) EBTKS has an I/O location that can be read to access the current internal value of PTR2. Although the issue for which it was created has now been resolved, this diagnostic read capability is still implemented, in case it may be needed in the future.

Full |

I/O Offset |

||

Address |

Octal |

Hex |

|

EBTKSPTR2 |

177760 |

360 |

0xF0 |